Terdapat 3 buah timer / counter pada ATMega8535 yaitu:

– 8 bit Timer / Counter 0 dengan PWM

– 16 bit Timer / Counter 1

– 8 bit Timer / Counter 2 dengan PWM dan Operasi Asinkron

8 bit Timer / Counter 0 dengan PWM

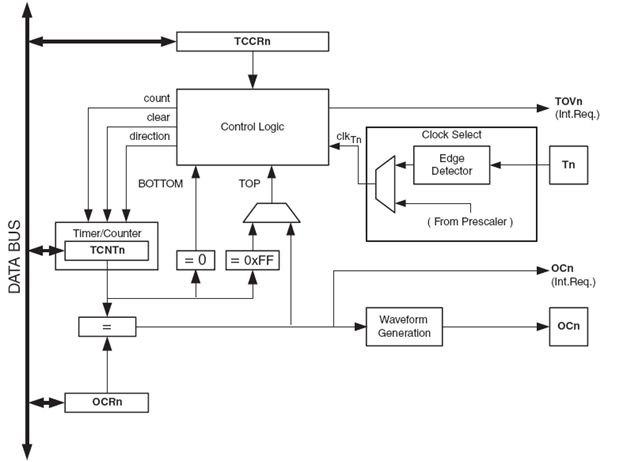

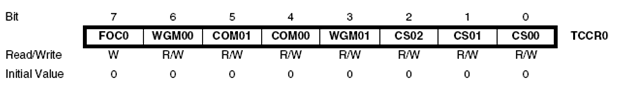

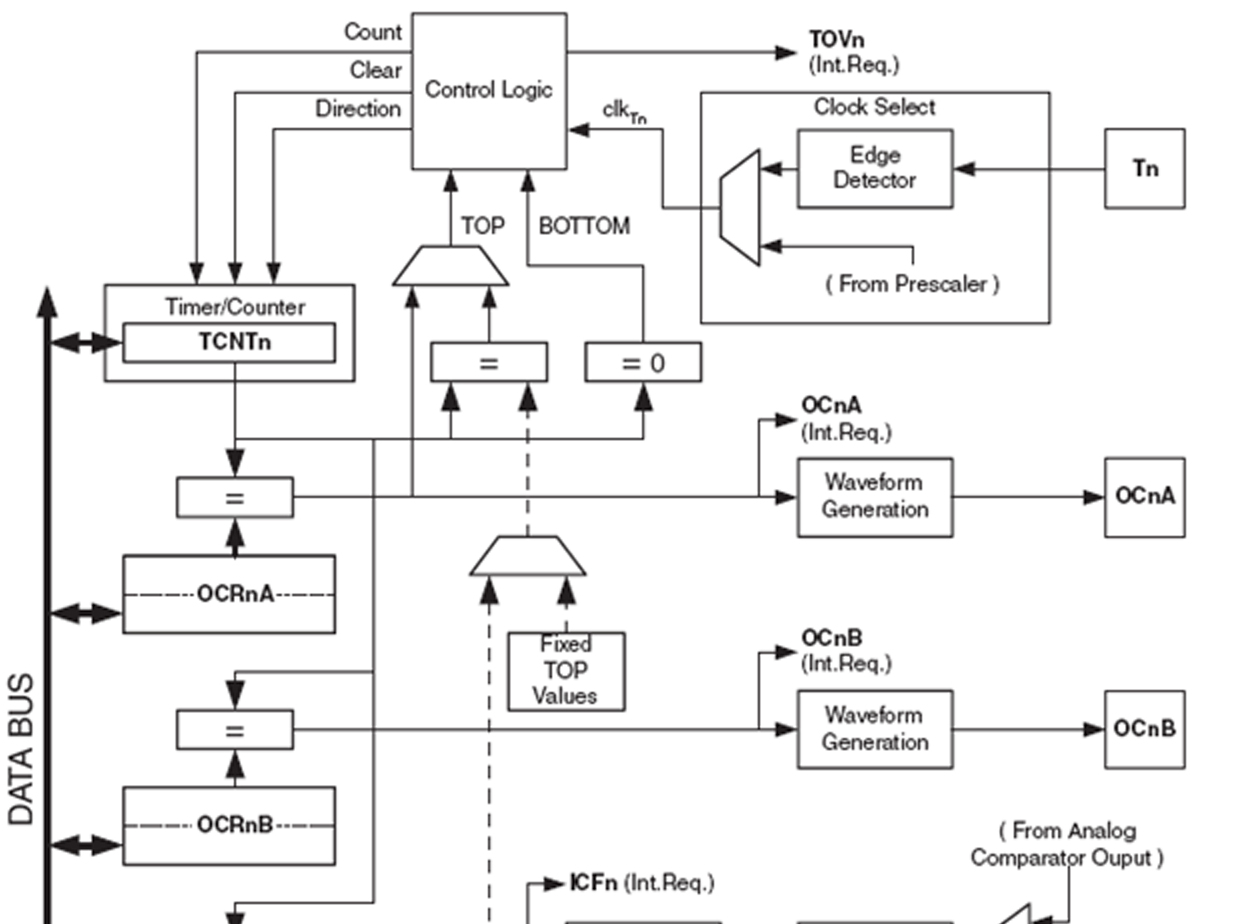

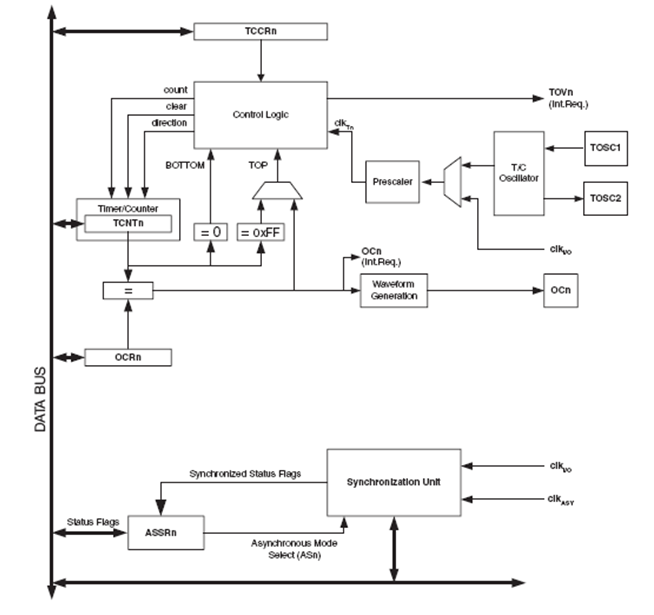

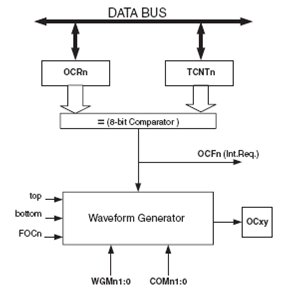

Gambar 5.1

TCNT0 dan OCR0 adalah 8 bit Register di mana keduanya akan dibandingkan dan dapat digunakan oleh Waveform Generation untuk membangkitkan PWM atau berbagai frekwensi pada pin OC0. Sumber clock dari counter dapat diambil dari External (T0) atau dari internal melalui Pre Scaler, hal ini diatur oleh Clock Select bit (CS2:0) yang ada di Register TCCR0.

TOV0 akan set tergantung dari mode operasi yang dipilih pada bit WGM01:0 di Register TCCR0. Flag ini juga dapat membangkitkan interupsi.

Pada saat TCNT0 dan OCR0 memperoleh nilai yang sama maka OCF0 akan set dan apabila Global Interrupt di SREG set dan OCIE0 bit = 1 maka output compare interrupt akan dibangkitkan.

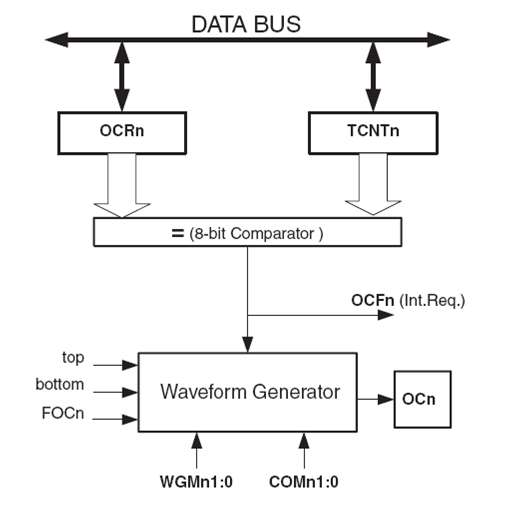

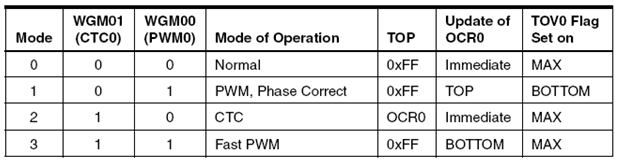

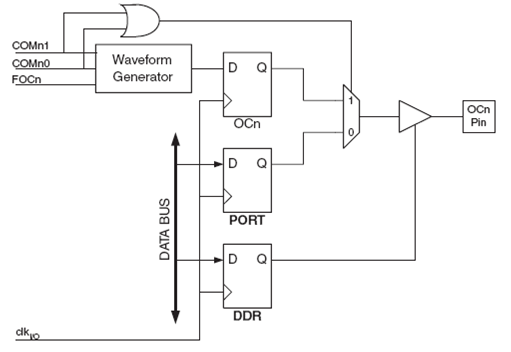

Gambar 5.2

Register OCR0 menggunakan sistem double buffer pada saat beroperasi Mode PWM, hal ini dibutuhkan agar tidak terjadi pulsa PWM yang tidak simetri atau noise (glitch) saat nilai OCR0 diupdate.

Force Output Compare

Pada mode selain PWM comparator bisa dipaksa untuk match walaupun belum mencapai nilai yang sesuai dengan menuliskan logika 1 di bit FOC0. Hal ini akan mempengaruhi pin OC0 namun tidak mempengaruhi OCF0 Flag ataupun reload / clear timer seperti pada saat comparator benar-benar mencapai nilai yang sama (match). Bit COM01:0 berfungsi untuk mengatur apakah OC0 akan Set, Clear atau toggle pada saat itu.

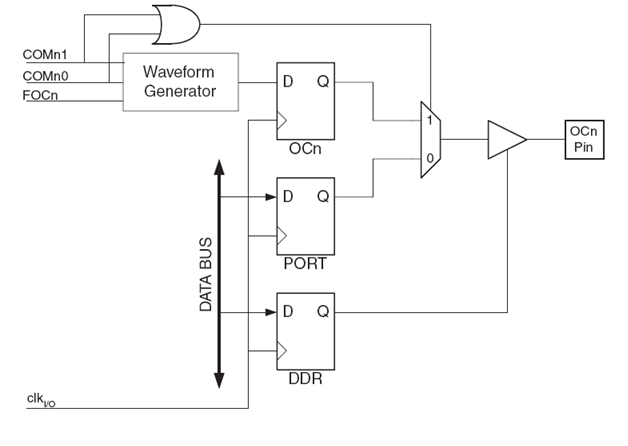

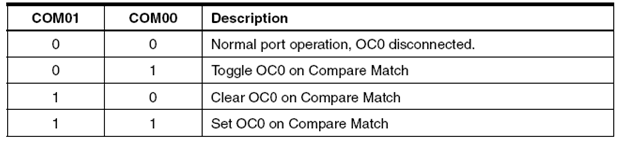

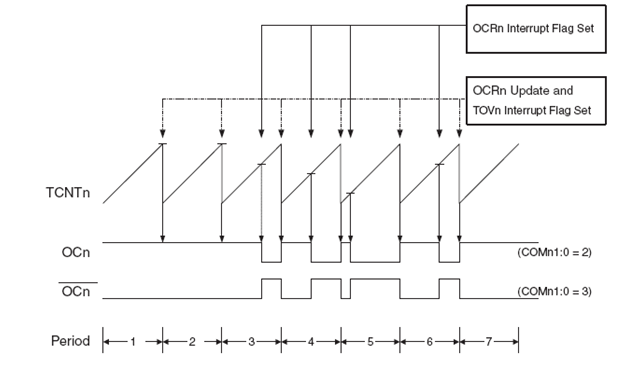

Gambar 5.3

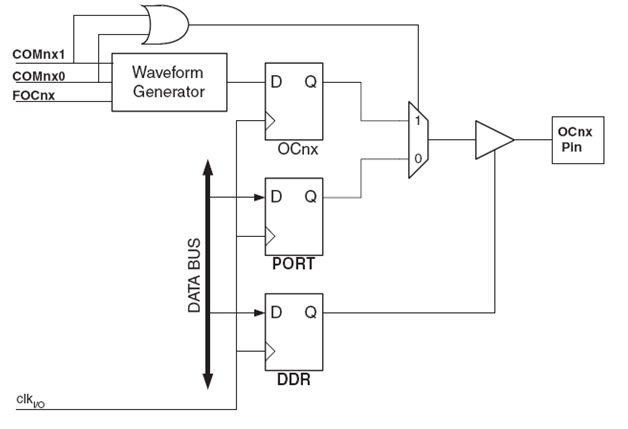

Compare Match Output Unit

Bit Compare Output Mode (COM01:0) memiliki dua fungsi yaitu mengatur Waveform Generator untuk menentukan kondisi OC0 pada saat Compare sesuai (match) atau mengendalikan pin OC0.

Namun pin OC0 masih tergantung oleh DDR pada port tersebut. DDR_OC0 terlebih dahulu harus diset sebagai output agar nilai OC0 dapat tampil di kaki OC0.

Mode Operasi

Pengaturan mode operasi timer ini dilakukan oleh bit WGM01:0 untuk waveform generation dan bit COM01:0 untuk Compare Output Mode. Berikut adalah mode-mode operasi tersebut.

Mode Normal (WGM01:0 = 0)

Mode ini adalah mode yang paling sederhana di mana counter akan menghitung naik hingga mencapai nilai 8 bit penuh yaitu 0xFF dan kembali lagi ke nol. TOV0 Flag akan set saat nilai counter kembali ke nol. Pada saat ini bagian output compare juga dapat membangkitkan interupsi apabila diaktifkan

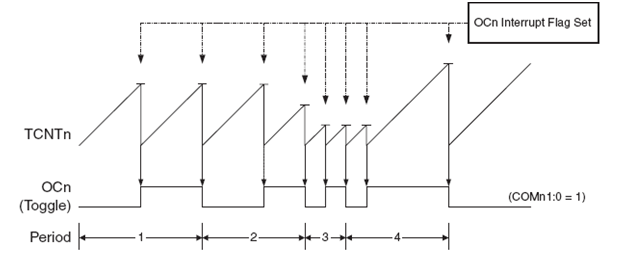

Mode Clear Time on Compare (CTC) (WGM01:0=2)

Pada mode ini counter akan clear ke nol saat mencapai nilai yang sama antara TCNT0 dan OCR0. Selain itu counter juga akan tetap kembali ke nol apabila mencapai nilai maksimum 0xFF. Pada saat counter kembali ke nol OC0 Flag akan aktif dan apabila Data Direction pada pin OC0 berfungsi sebagai output, maka OC0 akan bereaksi sesuai mode yang ditentukan oleh COM01:0. Frekwensi yang dihasilkan pada OC0 dapat dihitung dengan persamaan berikut.

Di mana N adalah faktor prescaler berupa bilangan (1, 8, 64, 256 atau 1024)

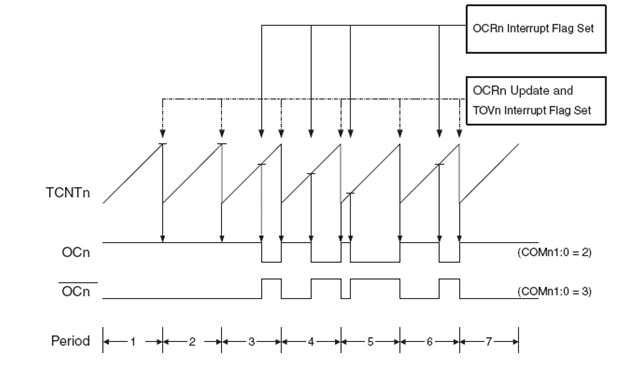

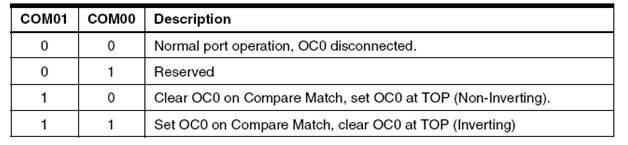

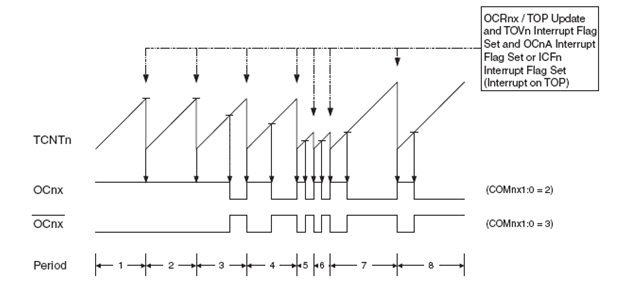

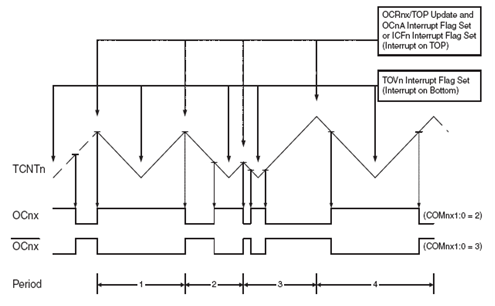

Mode Fast PWM

Mode ini akan menghasilkan PWM dengan frekwensi yang tinggi di mana counter akan menghitung dari nilai BOTTOM hingga TOP dan kembali lagi dari BOTTOBOTTOM. Timing Diagram pada mode ini tampak pada gambar di bawah ini.

Timer Overflow Flag akan selalu aktif saat counter mencapai nilai maksimal. Interupsi juga akan terjadi pada kondisi ini apabila bit pengatur interupsinya diaktifkan. Apabila bit COM01:0 = 2 maka signal non inverting akan muncul pada OC0, namun apabila bit COM01:0 = 3 maka signal inverting yang akan muncul pada OC0. Agar signal tersebut muncul pada kaki OC0, terlebih dahulu Data Direction dari OC0 harus diset satu yang berfungsi sebagai keluaran.

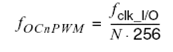

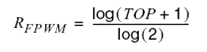

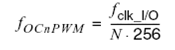

Frekwensi dari PWM yang dikeluarkan dapat dihitung dengan persamaan berikut:

N adalah faktor prescaler yang merupakan bilangan (1, 8, 64, 256 atau 1024)

Apabila nilai OCR0 diberi nilai yang extrem seperti nilai BOTTOM maka output dari OC0 akan berupa spike yang sangat kecil namun apabila diberi nilai TOP maka akan tampil pulsa high atau low yang sangat lebar tergantung dari kondisi bit COM01:0

Duty cycle 50% dapat diperoleh apabila bit COM01:0 diatur pada mode toggle.

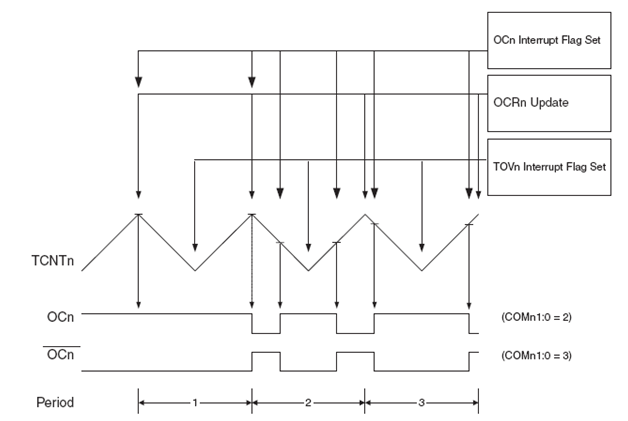

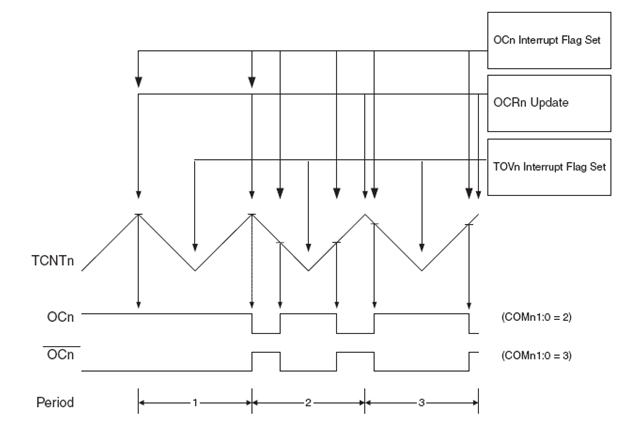

Phase Correct PWM Mode (WGM01:=1)

Pada mode ini, counter akan menghitung naik hingga nilai TOP dan kemudian menghitung turun hingga nilai terendah dan kembali lagi menghitung naik setelah nilai BOTTOM tercapai.

Pada Mode non inverting, kaki OC0 akan berubah menjadi low saat diperoleh nilai yang sama antara TCNT0 dan OCR0 pada saat counter naik dan berubah menjadi high apabila diperoleh nilai yang sama antara TCNT0 dan OCR0 pada saat counter turun. Hal yang sebaliknya terjadi apabila sedang dalam mode inverting.

Timer Overflow Flag akan selalu set pada setiap saat counter mencapai nilai BOTTOM. Interupsi dapat dibangkitkan pada saat ini apabila bit interupsi ini diaktifkan.

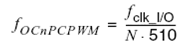

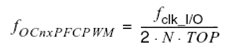

Frekwensi yang dihasilkan PWM dapat dihitung dengan persamaan berikut

N adalah factor prescaler dari bilangan (1, 64, 256 atau 1024)

Pemberian nilai yang ekstrem seperti nilai BOTTOM pada OCR0 akan mengakibatkan output pada OC0 berlogika nol terus menerus dan pemberian nilai TOP pada OCR0 akan mengakibatkan output pada OC0 berlogika 1 terus menerus.

Register-register Timer/Counter 0

Bit 7 – FOC0 Force Output Compare

FOC0 hanya aktif pada mode non PWM, namun sebaiknya tetap tuliskan 0 saja saat menulis data ke TCCR0 untuk menjaga kompatibilitas program dengan mikrokontroler AVR yang lain. Bit ini berfungsi untuk memaksa pin OC0 mengeluarkan output sesuai dengan mode yang ditentukan oleh bit CM01:0 walaupun proses compare belum match. Bit ini tidak akan membangkitkan interupsi ataupun berpengaruh pada TOV Flag.

Bit 6,3 – WGM01:0 Waveform Generation Mode

Bit ini berfungsi untuk mengatur mode dari Waveform Generation seperti pada tabel berikut

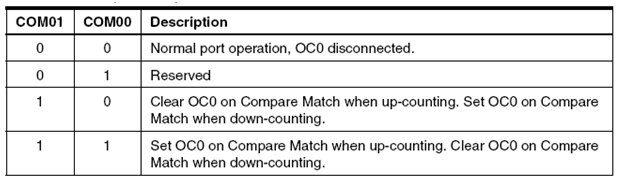

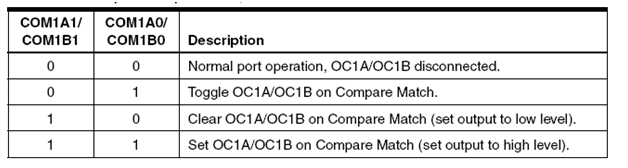

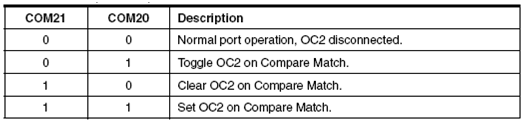

Bit 5,4 – CM01:0 Compare Match Output Mode

Bit ini berfungsi mengatur keluaran pada pin OC0 sesuai pada tabel-tabel berikut. Namun terlebih dahulu Data Direction pada OC0 harus diaktifkan sebagai keluaran.

Mode non PWM

Mode Fast PWM

Phase Correct PWM

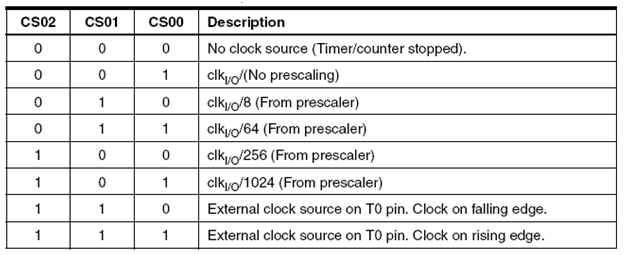

Bit 2:0 – CS02:0 Clock Select

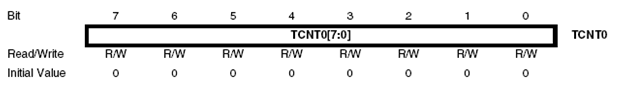

Timer/Counter Register TCNT0

Register ini dapat dibaca tulis secara langsung, penulisan data pada register ini akan mencegah nilai counter mencapai output match dengan OCR0. Oleh karena itu penulisan data pada register ini pada saat counter sedang berjalan mempunyai resiko adanya kehilangan kondisi output compare match.

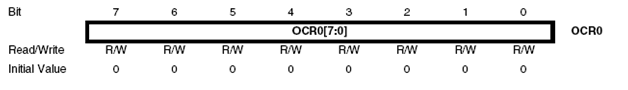

Output Compare Register – OCR0

Merupakan register yang digunakan sebagai pembanding dari TCNT0 di mana kondisi output compare match akan diperoleh saat TCNT0 memperoleh nilai yang sama.

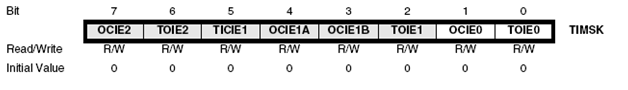

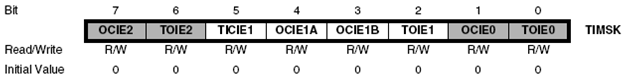

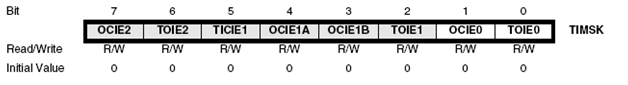

Register Timer/Counter Interrupt Mask – TIMSK

Bit 1 – OCIE0: Timer/Counter Output Compare Match Interrupt Enable

Saat bit ini di set 1 dan bit Global Interrupt Enable di SREG aktif maka interupsi akan terjadi saat counter mencapai nilai output compare match.

Bit 0 – TOIE0: Timer/Counter 0 Overflow Interrupt Enable

Saat bit ini di set 1 dan bit Global Interrupt Enable di SREG aktif maka interupsi akan terjadi saat counter mencapai nilai overflow

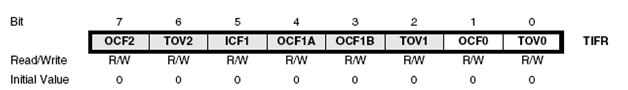

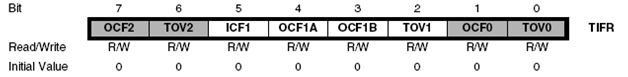

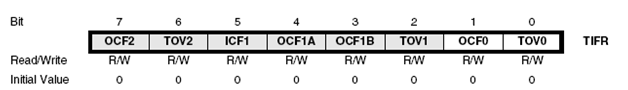

Register Timer/Counter Interrupt Flag – TIFR

Bit 1 – OCF0: Output Compare Flag 0

Bit ini akan set pada saat output compare match terjadi dan clear dengan sendirinya saat program menangani interupsi yang terjadi. Bit ini juga dapat clear dengan menuliskan logika 1 ke bit tersebut

Bit 0 – TOV0: Timer Overflow Flag 0

Bit ini akan set pada saat nilai overflow tercapai dan clear dengan sendirinya saat program menangani interupsi yang terjadi. Bit ini juga dapat clear dengan menuliskan logika 1 ke bit tersebut

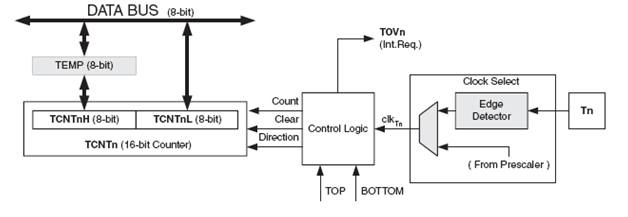

16 bit Timer / Counter 1

Pada timer/counter 1, register TCNT1, OCR1A, OCR1B dan ICR1 merupakan register 16 bit di mana dibutuhkan perlakuan khusus untuk mengaksesnya.

Pada penulisan ke register 16 bit dilakukan dengan diawali high byte terlebih dahulu dan dilanjutkan dengan low byte. Sedangkan untuk pembacaan diawali dengan pembacaan low byte terlebih dahulu dan dilanjutkan dengan high byte.

Sedangkan untuk Register TCCRnA dan TCCRnB di mana pada timer/counter 1 ini di mana n=1 maka register yang dimaksud adalah TCCR1A dan TCCR1B adalah merupakan register 8 bit dan tidak memerlukan perlakuan khusus untuk mengaksesnya.

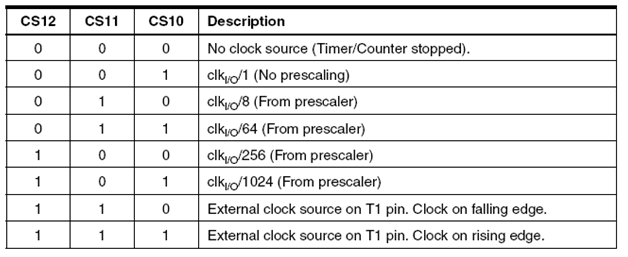

Timer dan counter ini dapat menerima clock internal melalui pre scaler atau external dari pin T1. Sumber clock ini diatur dari Clock Select Logic.

Register OCR1A dan OCR1B akan selalu dibandingkan dengan counter TCNT1 dan hasilnya akan diproses oleh Waveform Generator dan ditampilkan ke pin OC1 apabila Data Direction OC1 diset sebagai keluaran. Hasil perbandingan tersebut juga akan mempengaruhi OCF1A dan OCF1B apabila nilai TCNT1 mencapai nilai yang sama dengan OCR1A atau OCR1B

Untuk bagian Register Input Capture, register ini berfungsi sebagai penyimpan nilai counter yang dibangkitkan dengan sumber clock dari pin ICP1 atau juga dapat melalui Analog Comparator. Pin ICP1 ini juga memiliki noise canceler yang akan mereduksi noise yang diterima sehingga diperoleh perhitungan nilai counter yang akurat.

Timer/Counter Clock Sources

Timer/Counter dapat memperoleh clock dari external ataupun internal dan hal ini diatur oleh bit CS12:0 yang terletak pada Register TCCR1B.

Register TCNT1 yang menyimpan nilai counter adalah merupakan register 16 bit sehingga untuk mengaksesnya diperlukan perlakuan khusus yaitu dengan menuliskan high byte terlebih dahulu ke TCNT1H agar disimpan di TEMP dan selanjutnya low byte ke TCNT1L dan selanjutnya keduanya diteruskan ke TCNT1.

TOV1 akan set tergantung dari mode operasi yang dipilih pada bit WGM13:0 di Register TCCR1A dan TCCR1B. Flag ini juga dapat membangkitkan interupsi.

Global Interrupt di SREG set dan OCIE0 bit = 1 maka output compare interrupt akan dibangkitkan.

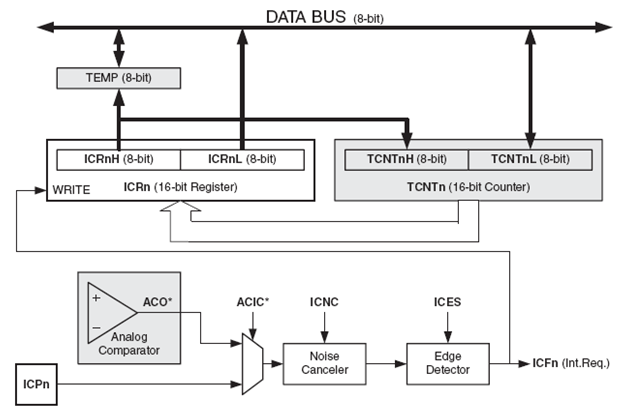

Input Capture Unit

Bagian ini dapat digunakan untuk aplikasi pengukuran frekwensi, duty cycle dan diambil melalui pin ICP1 atau dapat juga melalui analog comparator.

Pada saat terjadi perubahan pada pin ICP1 atau pada keluaran analog comparator (ACO) maka hal ini akan mentrigger Edge Detector sehingga nilai pada TCNT1 akan dituliskan pada ICR1. Hal ini akan mempengaruhi bit Flag ICF1 menjadi set. Bit ini akan clear otomatis saat program menangani interupsi yang terjadi atau dengan menuliskan logika 1 pada bit ini. Apabila pada saat itu bit TICIE1 = 1 dan global interrupt pada Register SREG = 1 maka interupsi akan terjadi.

Proses pembacaan ICR1 dilakukan dengan membaca low byte pada ICR1L terlebih dahulu dan dilanjutkan dengan high byte pada ICR1H.

Input Capture Trigger Source

Pada kondisi standard trigger dari ICP dilakukan melalui pin ICP1, namun untuk aplikasi tertentu hal ini juga dapat dilakukan melalui Analog Comparator Output sebagai sumber trigger yaitu dengan mengaktifkan bit ACIC di Register ACSR (Analog Comparator Status Register). Perlu diperhatikan bahwa perubahan ini dapat menimbulkan trigger juga oleh karena itu sebaiknya Input Capture Flag di clear setelah proses perubahan sumber trigger dilakukan.

Noise Canceler

Bagian ini berfungsi untuk mengatasi noise yang dapat mengakibatkan perhitungan counter melompat-lompat. Hal ini dilakukan dengan mengambil 4 kali sampel dan akan diperhitungkan apabila keempatnya memiliki nilai yang sama. Fungsi ini dapat diaktifkan dengan mengaktifkan bit ICNC1 Input Capture Noise Canceler di Register TCCR1B. Noise Canceler ini langsung mengambil dari sistem clock dan tidak terpengaruh oleh bagian prescaler

Penggunaan Input Capture

Pada penggunaan Input Capture ini perlu diperhatikan bahwa nilai dari ICR1 dapat berubah apabila terdapat trigger berikutnya. Oleh karena itu nilai dari ICR1 sebaiknya langsung segera diambil pada saat interupsi terjadi sebelum ICR1 berubah.

Setelah nilai ICR1 dibaca maka Flag ICF1 harus di clear secara manual dengan menuliskan logika 1 di bit ICF1. Kecuali untuk aplikasi pengukuran frekwensi, ICF1 ini tidak perlu diclear selama fungsi interupsinya digunakan.

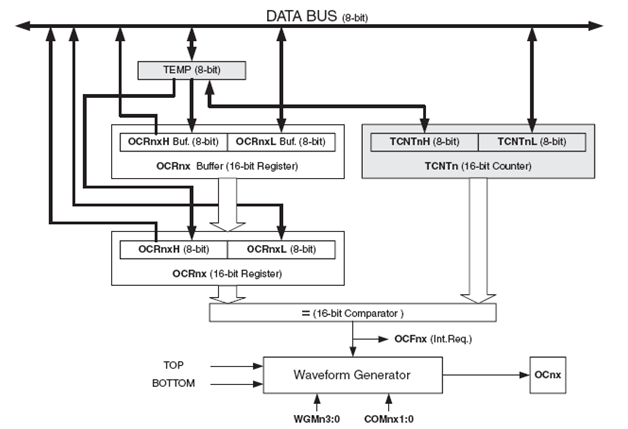

Output Compare Unit

16 bit comparator pada bagian ini akan selalu membandingkan nilai TCNT1 dengan OCR1x (x= a atau b) dan pada saat diperoleh hasil yang match maka bit OCF1x (x=a atau b) akan set. Bit ini akan dapat di clear secara manual dengan menuliskan logika 1 ke bit tersebut. Bit ini akan secara otomatis clear apabila fungsi interupsi diaktifkan dan program telah menuju ke vektor interupsi tersebut.

Waveform Generator akan menghasilkan output pada saat diperoleh kondisi match sesuai dengan mode yang ditentukan oleh bit WGM13:0 dan CM1x1:0.

OCR1x mempunyai double buffer, namun hal ini hanya berlaku pada mode PWM. Untuk Mode non PWM CPU mikrokontroler akan langsung mengakses ke Register OCR1x. Sedangkan pada Mode PWM di mana double buffer aktif, CPU akan mengakses ke Buffer OCR1x. Hal ini diperlukan untuk mencegah adanya pulsa yang tidak simetri atau glitch.

Penulisan data pada OCR1x dilakukan dengan diawali oleh high byte terlebih dahulu dan dilanjutkan dengan low byte.

Force Output Compare

Pada mode selain PWM comparator bisa dipaksa untuk match walaupun belum mencapai nilai yang sesuai dengan menuliskan logika 1 di bit FOC1. Hal ini akan mempengaruhi pin OC1 namun tidak mempengaruhi OCF1 Flag ataupun reload / clear timer seperti pada saat comparator benar-benar mencapai nilai yang sama (match). Bit COM11:0 berfungsi untuk mengatur apakah OC1 akan Set, Clear atau toggle pada saat itu.

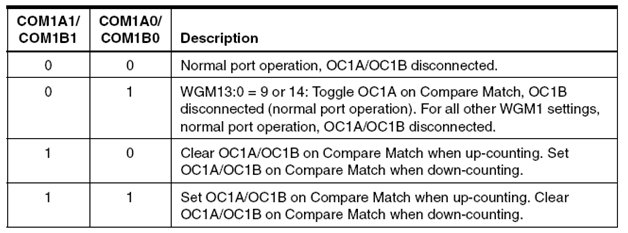

Compare Match Output Unit

Bit Compare Output Mode (COM11:0) memiliki dua fungsi yaitu mengatur Waveform Generator untuk menentukan kondisi OC1 pada saat Compare sesuai (match) atau mengendalikan pin OC1.

Namun pin OC1 masih tergantung oleh DDR pada port tersebut. DDR_OC1 terlebih dahulu harus diset sebagai output agar nilai OC1 dapat tampil di kaki OC1.

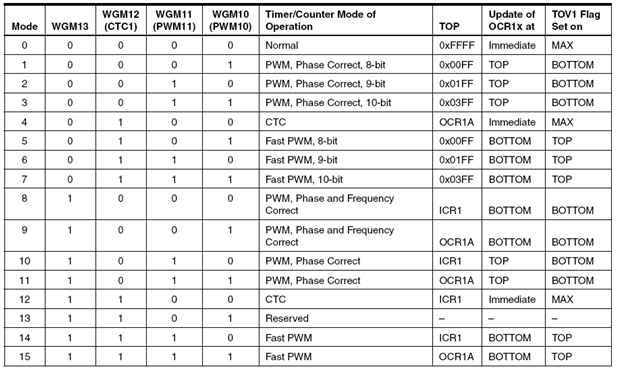

Mode Operasi

Pengaturan mode operasi timer ini dilakukan oleh bit WGM13:0 untuk waveform generation dan bit COM1x1:0 untuk Compare Output Mode. Berikut adalah mode-mode operasi tersebut.

Mode Normal (WGM13:0 = 0)

Mode ini adalah mode yang paling sederhana di mana counter akan menghitung naik hingga mencapai nilai 16 bit penuh yaitu 0xFFFF dan kembali lagi ke nol. TOV1 Flag akan set saat nilai counter kembali ke nol. Pada saat ini bagian output compare juga dapat membangkitkan interupsi apabila diaktifkan

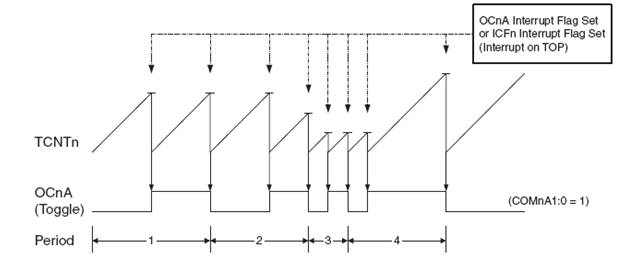

Mode Clear Time on Compare (CTC) (WGM013:0=4 atau 12)

Pada mode ini counter akan clear ke nol saat mencapai nilai yang sama antara TCNT1 dan OCR1x. Pada saat counter kembali ke nol OC1 Flag akan aktif dan apabila Data Direction pada pin OC1 berfungsi sebagai output, maka OC1 akan bereaksi sesuai mode yang ditentukan oleh COM13:0. Frekwensi yang dihasilkan pada OC1 dapat dihitung dengan persamaan berikut.

Di mana N adalah faktor prescaler berupa bilangan (1, 8, 64, 256 atau 1024)

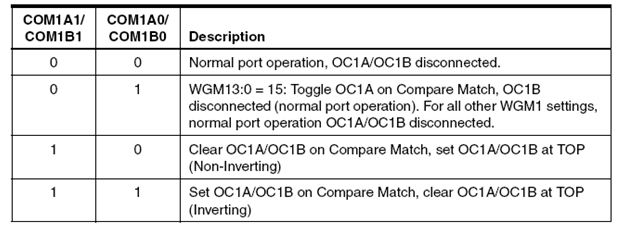

Mode Fast PWM

Mode ini akan menghasilkan PWM dengan frekwensi yang tinggi di mana counter akan menghitung dari nilai BOTTOM hingga TOP dan kembali lagi dari BOTTOM. Timing Diagram pada mode ini tampak pada gambar di bawah ini.

Timer Overflow Flag akan selalu aktif saat counter mencapai nilai maksimal. Interupsi juga akan terjadi pada kondisi ini apabila bit pengatur interupsinya diaktifkan. Pada mode non inverting OC1x akan set apabila TCNT1x dan OCR1x memperoleh nilai yang sama dan set saat mencapai nilai BOTTOM, namun pada mode Inverting OC1x akan clear apabila TCNT1x dan OCR1x memperoleh nilai yang sama dan clear apabila mencapai nilai BOTTOM. Agar signal tersebut muncul pada kaki OC0, terlebih dahulu Data Direction dari OC0 harus diset satu yang berfungsi sebagai keluaran.

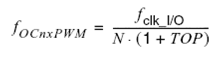

Resolusi dari PWM dapat diatur menjadi 8, 9, 10 bit atau ditentukan dari ICR1 atau OCR1A. Resolusi PWM dapat dihitung dengan menggunakan persamaan berikut

Pada mode ini, counter akan bertambah hingga mencapai nilai 0x00FF, 0x01FF atau 0x03FF (WGM13:0 = 5,6 atau 7), mencapai nilai pada ICR1 (WGM13:0 = 14) atau mencapai nilai OCR1A (WGM13:0 = 15). Counter kemudian akan reset pada clock berikutnya.

TOV1 akan set pada saat counter mencapai nilai TOP demikian juga flag OC1A atau ICF1 tergantung apakah OCR1A atau ICR1 yang digunakan untuk menentukan nilai TOP.

Saat mengatur nilai TOP, ada hal yang perlu diperhatikan yaitu nilai TOP jangan sampai di atas nilai OCR1x agar tidak terjadi kehilangan even output compare match.

Agar tidak terjadi kesalahan compare, pengisian ICR1 sebaiknya dilakukan pada saat di mana nilai TCNT1 berada di atas nilai yang akan diisikan di ICR1, hal ini disebabkan karena register ini tidak bersifat double buffer. Berbeda dengan OCR1x, register ini bersifat double buffer di mana nilai yang diisikan akan masuk ke OCR1 buffer terlebih dahulu dan akan diupdate pada clock selanjutnya setelah TCNT1 mencapai nilai TOP yaitu pada saat TCNT1 reset dan TOV1 Flag Set.

Pada mode ini signal PWM yang dibangkitkan pada pin OC1x akan tergantung dari bit COM1x1:0 dimana apabila COM1x1:0 = 2 maka nilai pada OC1x akan non inverting dan apabila COM1x1:0 = 3 maka nilai pada OC1 akan bersifat inverting.

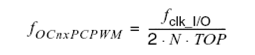

Berikut adalah persamaan untuk menghitung frekwensi yang dihasilkan oleh PWM

Variabel N adalah prescaler divider yaitu (1, 8, 64, 256 atau 1024)

Duty cycle 50% dapat diperoleh apabila bit COM11:0 diatur pada mode toggle.

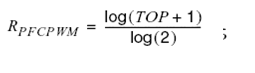

Mode Phase Correct PWM

Pada mode ini, counter akan menghitung naik hingga nilai TOP dan kemudian menghitung turun hingga nilai BOTTOM dan kembali lagi menghitung naik setelah nilai BOTTOM tercapai.

Pada Mode non inverting, kaki OC1x akan berubah menjadi low saat diperoleh nilai yang sama antara TCNT1 dan OCR1x pada saat counter naik dan berubah menjadi high apabila diperoleh nilai yang sama antara TCNT1 dan OCR1x pada saat counter turun. Hal yang sebaliknya terjadi apabila sedang dalam mode inverting.

Resolusi dari PWM dapat diatur menjadi 8, 9, 10 bit atau ditentukan dari ICR1 atau OCR1A.

Resolusi PWM dapat dihitung dengan menggunakan persamaan berikut

Pada mode ini, counter akan bertambah hingga mencapai nilai 0x00FF, 0x01FF atau 0x03FF (WGM13:0 = 1,2 atau 3), mencapai nilai pada ICR1 (WGM13:0 = 10) atau mencapai nilai OCR1A (WGM13:0 = 11). Counter kemudian akan reset pada clock berikutnya.

TOV1 akan selalu set setiap kali TCNT1 mencapai nilai BOTTOM. Saat OCR1A atau ICR1 digunakan untuk menentukan nilai TOP maka bit OC1A atau bit ICF1 flag akan set pada saat nilai OCR1x terupdate yaitu pada clock selanjutnya setelah TCNT1 mencapai nilai TOP.

Pada saat mengubah nilai TOP terlebih dahulu harus dipastikan bahwa nilai TOP harus lebih tinggi dari OCR1x, bila tidak maka compare match tidak akan pernah terpenuhi.

Pada mode ini signal yang dibangkitkan pada pin OC1x akan tergantung dari pengaturan bit COM1x1:0.

Pada saat COM1x1:0 = 2 maka output pada OC1x akan bersifat non inverting dan pada saat COM1x1:0 = 3 maka output pada OC1x akan bersifat inverting.

Berikut adalah persamaan yang digunakan untuk mengukur frekwensi dari PWM

N adalah prescaler divider yaitu (1, 8, 64, 256 atau 1024)

Duty cycle 50% dapat diperoleh apabila bit COM1A1:0 diatur pada mode toggle.

Phase and Frequency Correct PWM Mode (WGM13:0 = 8 atau 9)

Mode ini akan menghasilkan resolusi yang tinggi pada PWM waveform. Counter akan menghitung naik mulai dari BOTTOM (0x0000) hingga TOP dan kembali lagi turun hingga BOTTOM. Pada mode non inverting OC1x akan clear pada saat compare match terjadi antara TCNT1 dan OCR1x

Untuk resolusi PWM dapat dihitung dengan menggunakan persamaan berikut

Pada mode ini, counter akan naik hingga diperoleh nilai yang sesuai dengan ICR1 apabila WGM13:0 = 8 atau OCR1A apabila WGM13:0 = 9.

TOV1 akan selalu set pada saat OCR1x terupdate dengan double buffer valuenya, yaitu pada nilai BOTTOM. Saat OCR1A atau ICR1 digunakan sebagai penentu nilai TOP maka flag OC1A atau ICF1 akan set saat TCNT1 mencapai nilai TOP.

Flag interupsi dapat digunakan untuk membangkitkan interupsi saat nilai counter mencapai TOP atau BOTTOM.

Pada saat mengisi nilai TOP terlebih dahulu harus dipastikan bahwa nilai ini tidak lebih besar dari OCR1x bila tidak kondisi output compare match tidak akan pernah terpenuhi.

Pada mode ini signal yang dibangkitkan pada pin OC1x akan tergantung pada bit COM1x1:0. Apabila COM1x1:0 = 2 maka non inverting PWM akan muncul di OC1 dan apabila COM1x1:0=3 maka inverting PWm yang akan muncul di OC1.

Berikut adalah persamaan yang digunakan untuk menghitung frekwensi PWM

Variabel N adalah prescaler divider yaitu (1, 8, 64, 256 atau 1024)

Register-register yang digunakan

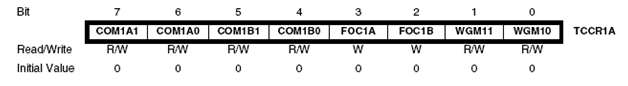

Timer/Counter1 Control Register – TCCR1A

Bit 7:6 – COM1A1:0 Compare Output Mode untuk channel A

Bit 5:4 – COM1B1:0 Compare Output Mode untuk channel B

Pada non PWM

Pada Fast PWM

Pada Phase Correct and Phase and Frequency Correct PWM

Bit 3 – FOC1A Force Output Compare untuk Channel A

Bit 2 – FOC1B Force Output Compare untuk Channel B

Bit 1:0 – WGM11:0 Waveform Generation Mode

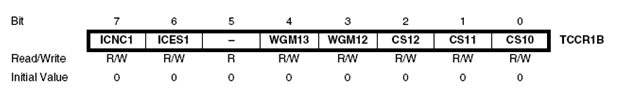

Timer/Counter1 Control Register B – TCCR1B

Bit 7 – ICNC1 Input Capture Noise Canceler

Dengan mengaktifkan bit ini maka signal yang masuk melalui ICP1 akan difilter untuk menghindari adanya noise

Bit 6 – ICES1 Input Capture Edge Select

Bit ini berfungsi untuk mengatur edge dari input capture di pin ICP1. Logika 0 berarti ICP1 = failing edge dan logika 1 berarti ICP1 = rising edge.

Bit 5 – reserve bit

Bit 4:3 – WGM13:2 Waveform Generaton Mode

Bit 2:0 – CS12:0 Clock Select

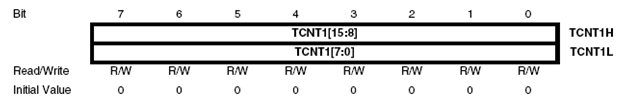

Timer/Counter1 – TCNT1H dan TCNT1L

Merupakan register 16 bit yang menyimpan nilai counter. Proses penulisan pada register ini dilakukan dengan menuliskan high byte terlebih dahulu ke TCNT1H dan dilanjutkan low byte di TCNT1L. Proses pembacaan dilakukan dengan membaca low byte terlebih dahulu dari TCNT1L dan kemudian dilanjutkan dengan high byte di TCNT1H.

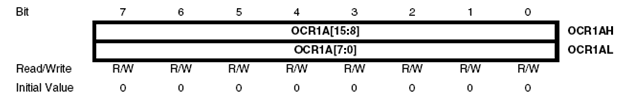

Output Compare Register 1A – OCR1AH dan OCR1AL

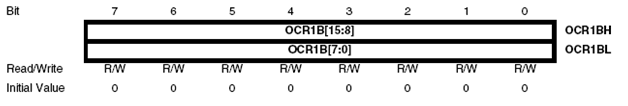

Output Compare Register 1B – OCR1BH dan OCR1BL

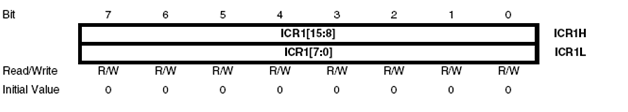

Input Capture register 1 – ICR1H dan ICR1L

Register ini akan terupdate dari nilai TCNT1 saat diperoleh signal dari pin ICP1 atau analog comparator. Selanjutnya register ini dapat digunakan untuk menentukan nilai TOP.

Timer / Counter Interrupt Mask Register – TIMSK

Bit 5 – TICIE1: timer / Counter 1 Input Capture Interrupt Enable

Logika 1 pada bit ini akan mengaktifkan interupsi input capture apabila bit Global Interrupt di SREG aktif

Bit 4 – OCIE1A: Timer / Counter 1 Output Compare A Match Interrupt Enable

Logika 1 pada bit ini akan mengaktifkan interupsi output compare A apabila bit Global Interrupt di SREG aktif

Bit 3 – OCIE1B: Timer / Counter 1 Output Compare B Match Interrupt Enable

Logika 1 pada bit ini akan mengaktifkan interupsi output compare B apabila bit Global Interrupt di SREG aktif

Bit 2 – TOIE1: Timer / Counter 1 Overflow Interrupt Enable

Logika 1 pada bit ini akan mengaktifkan interupsi Counter1 overflow apabila bit Global Interrupt di SREG aktif

Timer / Counter Interrupt Flag Register – TIFR

Bit 5 – ICF1 Timer / Counter 1 Input Capture Flag

Flag ini akan set saat signal pada pin ICP1 diterima dan otomatis clear saat Input Capture Interrupt Vector dieksekusi. Bit ini juga dapat di clear secara manual dengan menuliskan logika 1 pada bit ini.

Bit 4 – OCF1A Timer / Counter 1 Output Compare A Match Flag

Flag ini akan set pada saat output compare A match dan clear saat output compare A Match interrupt vector dieksekusi. Bit ini juga dapat di clear secara manual dengan menuliskan logika 1 pada bit ini.

Bit 3 – OCF1B Timer / Counter 1 Output Compare B Match Flag

Flag ini akan set pada saat output compare B match dan clear saat output compare A Match interrupt vector dieksekusi. Bit ini juga dapat di clear secara manual dengan menuliskan logika 1 pada bit ini.

Bit 2 – TOV1 Timer / Counter 1 Overflow Flag

Pada mode normal dan CTC TOV1 Flag akan set saat timer overflow. Bit ini akan otomatis clear saat timer / Counter 1 Overflow Interrupt Vector dieksekusi. Bit ini juga dapat di clear secara manual dengan menuliskan logika 1 pada bit ini.

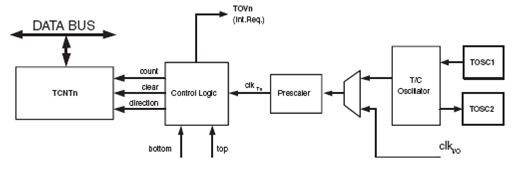

8 bit Timer / Counter 2 with PWM and Asynchronous Operation

Timer dan counter dapat memperoleh clock secara internal melalui prescaler atau secara asinkron melalui kaki TOSC ½. Mode Asinkron ini diatur oleh Register ASSR.

Register OCR2 yang bersifat double buffer akan membandingkan nilainya dengan TCNT2 dan hasilnya akan digunakan oleh Waveform generator untuk membangkitkan sinyal PWM atau frekwensi yang bervariasi pada pin OC2. Pada saat diperoleh kondisi match maka OCF2 akan set dan interupsi akan terjadi apabila Output Compare Match Interrupt aktif.

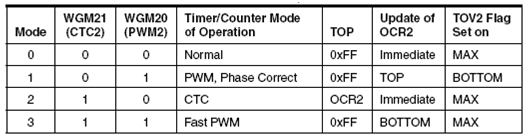

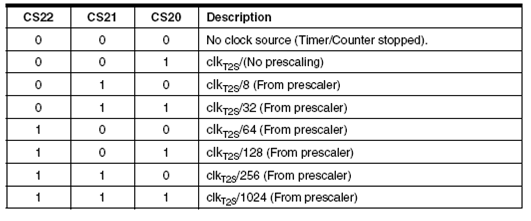

Untuk memilih sumber clock dari counter ini dapat dilakukan dengan mengatur bit CS22:0 (Clock Select Bit). Proses perhitungan counter diatur oleh bit WGM20 dan WGM21 yang terletak pada TCCR2 yang menentukan bagaimana gelombang yang akan dibangkitkan pada kaki OC2.

Timer Overflow Flag TOV2 akan set berdasarkan mode yang dipilih pada bit WGM21:0 dan dapat membangkitkan interupsi apabila Timer 2 Overflow Interrupt diaktifkan.

Output Compare Unit

8 bit comparator pada bagian ini akan selalu membandingkan nilai TCNT2 dengan OCR2 dan pada saat diperoleh hasil yang match maka bit OCF2 akan set. Bit ini akan dapat di clear secara manual dengan menuliskan logika 1 ke bit tersebut. Bit ini akan secara otomatis clear apabila fungsi interupsi diaktifkan dan program telah menuju ke vektor interupsi tersebut.

Waveform Generator akan menghasilkan output pada saat diperoleh kondisi match sesuai dengan mode yang ditentukan oleh bit WGM21:0 dan CM21:0.

OCR2 mempunyai double buffer, namun hal ini hanya berlaku pada mode PWM. Untuk Mode non PWM CPU mikrokontroler akan langsung mengakses ke Register OCR1x. Sedangkan pada Mode PWM di mana double buffer aktif, CPU akan mengakses ke Buffer OCR2. Hal ini diperlukan untuk mencegah adanya pulsa yang tidak simetri atau glitch.

Force Output Compare

Pada mode selain PWM comparator bisa dipaksa untuk match walaupun belum mencapai nilai yang sesuai dengan menuliskan logika 1 di bit FOC2. Hal ini akan mempengaruhi pin OC0 namun tidak mempengaruhi OCF2 Flag ataupun reload / clear timer seperti pada saat comparator benar-benar mencapai nilai yang sama (match). Bit COM21:0 berfungsi untuk mengatur apakah OC2 akan Set, Clear atau toggle pada saat itu.

Compare Match Output Unit

Bit Compare Output Mode (COM21:0) memiliki dua fungsi yaitu mengatur Waveform Generator untuk menentukan kondisi OC2 pada saat Compare sesuai (match) atau mengendalikan pin OC2.

Namun pin OC2 masih tergantung oleh DDR pada port tersebut. DDR_OC2 terlebih dahulu harus diset sebagai output agar nilai OC2 dapat tampil di kaki OC2.

Mode Operasi

Pengaturan mode operasi timer ini dilakukan oleh bit WGM21:0 untuk waveform generation dan bit COM21:0 untuk Compare Output Mode. Berikut adalah mode-mode operasi tersebut.

Mode Normal (WGM21:0 = 0)

Mode ini adalah mode yang paling sederhana di mana counter akan menghitung naik hingga mencapai nilai 8 bit penuh yaitu 0xFF dan kembali lagi ke nol. TOV2 Flag akan set saat nilai counter kembali ke nol. Pada saat ini bagian output compare juga dapat membangkitkan interupsi apabila diaktifkan

Mode Clear Time on Compare (CTC) (WGM01:0=2)

Pada mode ini counter akan clear ke nol saat mencapai nilai yang sama antara TCNT2 dan OCR2. Selain itu counter juga akan tetap kembali ke nol apabila mencapai nilai maksimum 0xFF. Pada saat counter kembali ke nol OC2 Flag akan aktif dan apabila Data Direction pada pin OC2 berfungsi sebagai output, maka OC2 akan bereaksi sesuai mode yang ditentukan oleh COM21:0. Frekwensi yang dihasilkan pada OC2 dapat dihitung dengan persamaan berikut.

![]()

Di mana N adalah faktor prescaler berupa bilangan (1, 8, 64, 256 atau 1024)

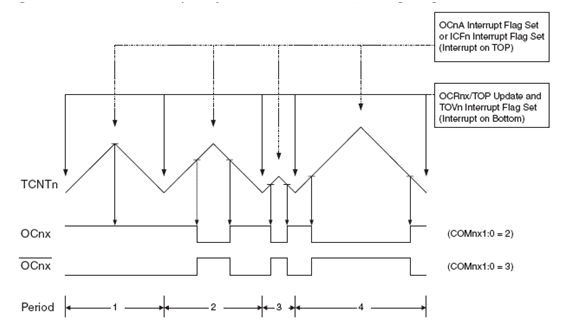

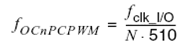

Mode Fast PWM (WGM21:0 = 3)

Mode ini akan menghasilkan PWM dengan frekwensi yang tinggi di mana counter akan menghitung dari nilai BOTTOM hingga TOP dan kembali lagi dari BOTTOBOTTOM. Timing Diagram pada mode ini tampak pada gambar di bawah ini.

Timer Overflow Flag akan selalu aktif saat counter mencapai nilai maksimal. Interupsi juga akan terjadi pada kondisi ini apabila bit pengatur interupsinya diaktifkan. Apabila bit COM21:0 = 2 maka signal non inverting akan muncul pada OC2, namun apabila bit COM21:0 = 3 maka signal inverting yang akan muncul pada OC2. Agar signal tersebut muncul pada kaki OC2, terlebih dahulu Data Direction dari OC2 harus diset satu yang berfungsi sebagai keluaran.

Frekwensi dari PWM yang dikeluarkan dapat dihitung dengan persamaan berikut:

N adalah faktor prescaler yang merupakan bilangan (1, 8, 64, 256 atau 1024)

Apabila nilai OCR2 diberi nilai yang extrem seperti nilai BOTTOM maka output dari OC2 akan berupa spike yang sangat kecil namun apabila diberi nilai TOP maka akan tampil pulsa high atau low yang sangat lebar tergantung dari kondisi bit COM21:0

Duty cycle 50% dapat diperoleh apabila bit COM21:0 diatur pada mode toggle.

Phase Correct PWM Mode (WGM21:=1)

Pada mode ini, counter akan menghitung naik hingga nilai TOP dan kemudian menghitung turun hingga nilai terendah dan kembali lagi menghitung naik setelah nilai BOTTOM tercapai.

Pada Mode non inverting, kaki OC2 akan berubah menjadi low saat diperoleh nilai yang sama antara TCNT2 dan OCR2 pada saat counter naik dan berubah menjadi high apabila diperoleh nilai yang sama antara TCNT2 dan OCR2 pada saat counter turun. Hal yang sebaliknya terjadi apabila sedang dalam mode inverting.

Timer Overflow Flag akan selalu set pada setiap saat counter mencapai nilai BOTTOM. Interupsi dapat dibangkitkan pada saat ini apabila bit interupsi ini diaktifkan.

Frekwensi yang dihasilkan PWM dapat dihitung dengan persamaan berikut

N adalah factor prescaler dari bilangan (1, 64, 256 atau 1024)

Pemberian nilai yang ekstrem seperti nilai BOTTOM pada OCR2 akan mengakibatkan output pada OC2 berlogika nol terus menerus dan pemberian nilai TOP pada OCR2 akan mengakibatkan output pada OC2 berlogika 1 terus menerus.

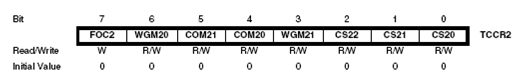

Register-register yang digunakan

Timer / Counter Control Register – TCCR2

Bit 7 – FOC2 Force Output Compare

FOC0 hanya aktif pada mode non PWM, namun sebaiknya tetap tuliskan 0 saja saat menulis data ke TCCR0 untuk menjaga kompatibilitas program dengan mikrokontroler AVR yang lain. Bit ini berfungsi untuk memaksa pin OC0 mengeluarkan output sesuai dengan mode yang ditentukan oleh bit CM01:0 walaupun proses compare belum match. Bit ini tidak akan membangkitkan interupsi ataupun berpengaruh pada TOV Flag.

Bit 6,3 – WGM21:0 Waveform Generation Mode

Bit ini berfungsi untuk mengatur mode dari Waveform Generation seperti pada tabel berikut

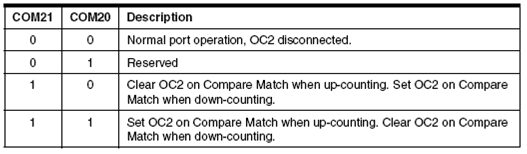

Bit 5,4 – CM21:0 Compare Match Output Mode

Bit ini berfungsi mengatur keluaran pada pin OC2 sesuai pada tabel-tabel berikut. Namun terlebih dahulu Data Direction pada OC2 harus diaktifkan sebagai keluaran.

Mode non PWM

Mode Fast PWM

Phase Correct PWM

Bit 2:0 – CS02:0 Clock Select

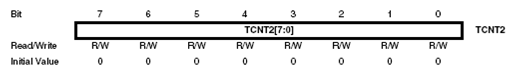

Timer/Counter Register TCNT2

Register ini dapat dibaca tulis secara langsung, penulisan data pada register ini akan mencegah nilai counter mencapai output match dengan OCR2. Oleh karena itu penulisan data pada register ini pada saat counter sedang berjalan mempunyai resiko adanya kehilangan kondisi output compare match.

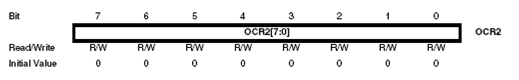

Output Compare Register – OCR2

Merupakan register yang digunakan sebagai pembanding dari TCNT2 di mana kondisi output compare match akan diperoleh saat TCNT2 memperoleh nilai yang sama.

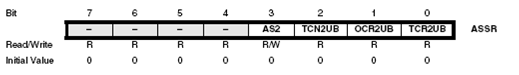

Asynchronous Status Register – ASSR2

Bit 3 – AS2 Asynchronous Timer / Counter 2

Saat AS2 = 0 maka timer / counter akan mendapat clock dari internal namun apabila AS2=1 maka timer/counter akan mendapat clock dari external melalui pin TOSC1. Pada saat perubahan nilai pada AS2 maka TCNT2, OCR2 dan TCCR2 mungkin juga akan berubah.

Bit 2 – TCN2UB Timer / Counter 2 Update Busy

Bit ini akan set apabila ada penulisan data di TCNT2 dan akan clear saat nilai TCNT2 diupdate ke temporary. Fungsi bit ini adalah mendeteksi apakah TCNT2 siap untuk menerima nilai baru dengan adanya kondisi logika 0 pada bit ini.

Bit 1 – OCR2UB Output Compare Register 2 Update Busy

Bit ini akan set apabila ada penulisan data di OCR2 dan akan clear saat nilai OCR2 diupdate ke temporary. Fungsi bit ini adalah mendeteksi apakah OCR2 siap untuk menerima nilai baru dengan adanya kondisi logika 0 pada bit ini.

Bit 0 – TCR2UB Timer/Counter Control Register 2 Update Busy

Bit ini akan set apabila ada penulisan data di TCCR2 dan akan clear saat nilai TCCR2 diupdate ke temporary. Fungsi bit ini adalah mendeteksi apakah TCCR2 siap untuk menerima nilai baru dengan adanya kondisi logika 0 pada bit ini.

Mekanisme untuk membaca nilai TCNT2, OCR2 dan TCCR2 agak berbeda. Saat membaca TCNT2 nilai aktual timer akan langsung terbaca namun saat membaca OCR2 dan TCCR2 maka nilai pada register temporary yang akan terbaca.

Hal-hal yang perlu diperhatikan saat menggunakan Asynchronous Operation of Timer / Counter 2.

– Saat mengubah sumber clock register TCNT2, TCCR2 dan OCR2 mungkin akan berubah oleh karena itu sebaiknya hal-hal berikut yang perlu dilakukan

- Disable semua Timer / Counter 2 interrupt dengan clear bit OCIE2 dan TOIE2

- Atur bit sumber clock dengan mengatur bit AS2

- Tulis nilai baru pada TCNT2, TCCR2 dan OCR2

- Sebelum pindah ke mode asinkron, tunggu bit TCN2UB, OCR2UB dan TCR2UB siap

- Clear Flag Timer / Counter Interrupt 2

- Aktifkan kembali interupsi bila memang diperlukan

– Gunakan osilator yang minimal 4 kali dibawah frekwensi clock CPU ATMega8535

– Saat menuliskan data ke TCNT2, TCCR2 atau OCR2 pastikan kondisi bit TCN2UB, TCR2UB atau OCR2UB tidak sedang sibuk

– Pada saat masuk ke mode power save atau standby, apabila sebelumnya terdapat proses penulisan ke TCNT2, TCCR2 atau OCR2 maka pastikan kondisi bit TCN2UB, TCR2UB atau OCR2UB tidak sedang sibuk

– Apabila dibutuhkan aplikasi untuk wake up dari mode power save atau standby maka harus diatur agar waktu yang dari power save atau standby ke wake up tidak boleh dibawah 1 siklus TOSC1 karena akan mengakibatkan kegagalan untuk wake up

– Pada mode asinkron ini osilator 32.768 KHz akan selalu aktif kecuali pada saat mode power save atau standby. Saat wake up dari mode tersebut osilator ini akan membutuhkan waktu selama satu detik sebelum memperoleh nilai yang stabil.

– Saat wake up dari mode power save atau standby, mikrokontroler membutuhkan waktu sekitar 4 siklus sebelum mengeksekusi interupsi atau meneruskan kerja program.

– Pada saat wake up dari mode power save atau standby, pembacaan data pada TCNT2 kemungkinan akan salah, oleh karena itu sebaiknya dilakukan prosedur berikut

- Tulis nilai apa saja ke OCR2 atau TCCR2

- Tunggu sampai flag busy ready

- Baca nilai TCNT2

– Pada mode asinkron, sinkronisasi interupsi flag membutuhkan 3 kali siklus mesin + 1 kali siklus timer. Setelah proses ini baru nilai timer dapat dibaca saat terjadi interupsi.

Register Timer/Counter Interrupt Mask – TIMSK

Bit 1 – OCIE2: Timer/Counter Output Compare Match Interrupt Enable

Saat bit ini di set 1 dan bit Global Interrupt Enable di SREG aktif maka interupsi akan terjadi saat counter mencapai nilai output compare match.

Bit 0 – TOIE2: Timer/Counter 0 Overflow Interrupt Enable

Saat bit ini di set 1 dan bit Global Interrupt Enable di SREG aktif maka interupsi akan terjadi saat counter mencapai nilai overflow

Register Timer/Counter Interrupt Flag – TIFR

Bit 1 – OCF2: Output Compare Flag 2

Bit ini akan set pada saat output compare match terjadi dan clear dengan sendirinya saat program menangani interupsi yang terjadi. Bit ini juga dapat clear dengan menuliskan logika 1 ke bit tersebut

Bit 0 – TOV2: Timer Overflow Flag 2

Bit ini akan set pada saat nilai overflow tercapai dan clear dengan sendirinya saat program menangani interupsi yang terjadi. Bit ini juga dapat clear dengan menuliskan logika 1 ke bit tersebut

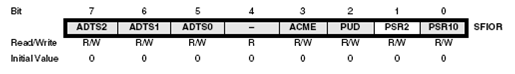

Special Function I/O Register – SFIOR

Bit 1 – PSR2 Prescaler Reset Timer / Counter 2

Pada saat bit ini ditulis dengan logika 1 maka prescaler Timer / Counter 2 akan reset. Bit ini akan clear otomatis setelah operasi dilakukan. Bit ini akan selalu terbaca 0 apabila timer / counter menggunakan internal clock.

Contoh Program

#include<avr/io.h>

Listing 5.1

Program membangkitkan PWM resolusi 10 bit di OC1A

int main(void){

DDRD=0xFF;

TCCR1A=(1<<COM1A1)|(0<<COM1A0)|(0<<COM1B1)|(0<<COM1B0)|(1<<WGM11)|(1<<WGM10);

TCCR1B=(0<<ICNC1) |(0<<ICES1) |(0<<WGM13) |(0<<WGM12) |(1<<CS12) |(0<<CS11) | (0<<CS10);

TCNT1=0;

OCR1A=0x0180;

}

Register TCCR1A dan TCCR1B diatur pada mode OC1A clear saat compare match dan WGM13:0 mode resolusi 10 bit.

Kemudian nilai 0x180 adalah nilai tengah pada PWM resolusi 10 bit oleh karena itu akan diperoleh sinyal duty cycle 50% pada output PWM. Dengan memperbesar nilai OCR1A maka level high akan semakin besar dan level low semakin kecil.

Listing 5.2

Program menghitung jumlah pulsa yang masuk di pin ICP1

#include<avr/io.h>

int main(void){

DDRD=0b101111;

DDRB=0b111111;

TCCR1B=(1<<ICNC1) |(0<<ICES1) |(0<<WGM13) |(0<<WGM12) |(1<<CS12) |(0<<CS11) | (0<<CS10);

while(1)

PORTB=ICR1;

}

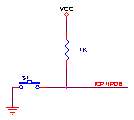

Hubungkan saklar push on dan resistor pull up seperti pada gambar berikut pada ICP1/PD6 dan pasang 8 bit LED Logic Tester pada Port B. Tekan saklar tersebut dan nilai pada 8 bit LED Logic Tester akan bertambah. Karena penekanan mekanik menimbulkan bouncing maka counter akan terlihat melompat.

DELTA ELECTRONIC

Paulus Andi Nalwan, ST